大家好,欢迎来到IT知识分享网。

1、DDR SDRAM 芯片的工作原理

DDR SDRAM是一种高速CMOS双倍数据率的同步动态随机存储器,其特点是集成度高、密度大、接口带宽高,价格便宜。

与传统的SDR SDRAM不同的是,DDR SDRAM采用双数据速率端口,在时钟的正沿和负沿都需要对数据进行采样,是一种2-n预取(2-n Prefetch)结构,即每个时钟周期数据传输率为2nbit。

由于DDR SDRAM的频率很高,如果采用传统的系统同步的方式会导致时序的紧张。因此DDR SDRAM采用源同步的传输方式,读写数据的采样均由随路传送的时钟(DQS)来进行。在读数据的时候,由存储器在送出有效数据DQ的同时将有效的DQS采样信号送出;在写数据的时候,由FPGA送出相应的数据DQ和DQS。源同步的方法使得采样时钟和数据之间有确定的相位关系,从而使得采样的时序余量最大化。

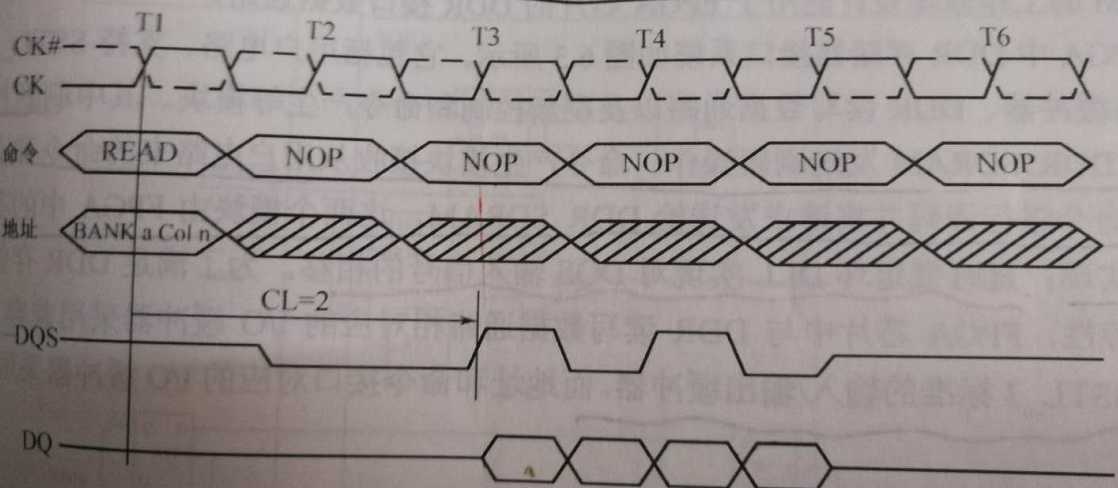

DDR SDRAM中的读和写访问是突发模式,读写访问从一个选定的地址开始,并以编程好的顺序连续存取,存取的长度是DDR SDRAM中设定的突发长度。在读的时候数据采样信号(DQS)和数据总线(DQ)在命令有效的CK/CK#正沿后一个CAS延迟(CAS Latency,CL)之后有效,如下图所示 表示当CL=2时,DDR SDRAM的读写时序关系,突发长度(Burst Length,BL)为4。系统时钟的上升沿T1给DDR SDRAM输入READ命令和相应的BANK和地址,DDR存储器在系统时钟上升沿T3输出DQS和DQ信号。从READ命令发出到有效数据出现在总线上的这段时间叫做CAS延迟。发出命令后总线上送出4个数据,是由数据突发长度BL决定的,因为途中BL=4,所以在一个READ命令后总线上会送出4个数据。BL和CL通过配置DDR存储器中模式寄存器来改变。伴随DQS信号和DQ同步送出,因为DQ和DQS是边沿对齐,无法用DQS信号直接去采样DQ,所以在控制器设计中必须用延时90°相位后的DQS信号来锁存DQ信号。

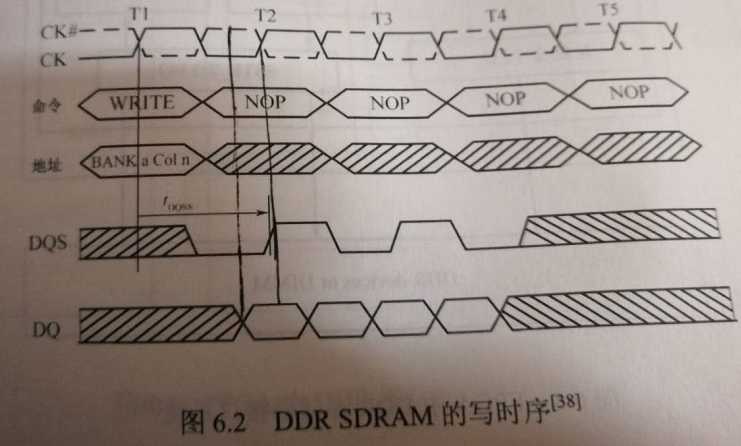

下图是CL=2、BL=4时的DDR SDRAM的写操作时序关系图,控制器在系统时钟的上升沿T1给DDR SDRAM输入WRITE命令和相应的BANK和地址,DQS的第一个上升沿出现在WRITE命令的下一个系统时钟正沿处,这一段时间定义为tDQSS,它的有效范围是一个时钟周期的75%~125%。写操作时的DQS和DQ数据是中间对齐的,这样送给DDR SDRAM芯片后,DQS能够直接采样DQ信号。

2.FPGA芯片中DDR存储器接口系统设计

FPGA通常内嵌有存储器块,但一般其存储容量不大。当FPGA用户设计的系统需要有大量的数据存储和读写时,需要用到片外DDR存储器,这时FPGA芯片需要有与外部存储器的高速接口。

FPGA芯片中的DDR存储器接口是为FPGA用户电路提供对片外的DDR SDRAM的访问控制。这一节介绍DDR SDRAM芯片的工作原理,并根据DDR SDRAM的工作原理设计适用于FPGA芯片的DDR接口数据通路。

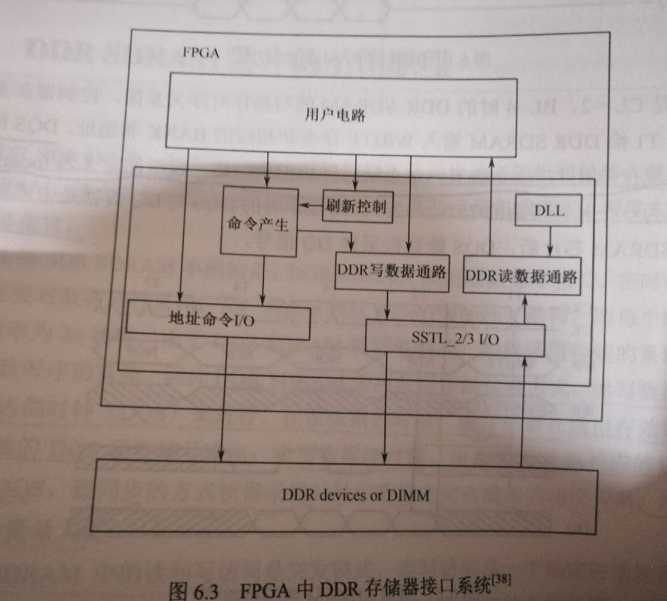

FPGA中DDR存储器接口系统如下图:它包括用户电路、支持SSTL–2/3的输入/输出缓冲器、DDR读写数据通路以及刷新控制和命令产生模块。

其中刷新控制模块定时为DDR SDRAM发送刷新操作,命令产生模块接收从用户电路来的命令和存储器地址,对命令进行译码并将请求发送给DDR SDRAM,这两个模块由于FPGA中国的芯核可编程资源实现;延时锁定环DDL实现对DQS输入信号的相移。为了满足DDR 存储器即可的电器特性,FPGA芯片中与DDR读写数据通路相对应I/O缓冲器采用兼容SSTL_2标准和SSTL_3标准的输入/输出缓冲器,而地址和命令接口对应的I/O缓冲器采用LVTTL标准。

2.1DDR接口的数据通路

由于DDR接口的工作频率较高,若采用传统的系统同步,会导致时序紧张,因此DDR接口采用源同步的方式,即数据信号和采样信号伴随传输,保持一定的相位关系。

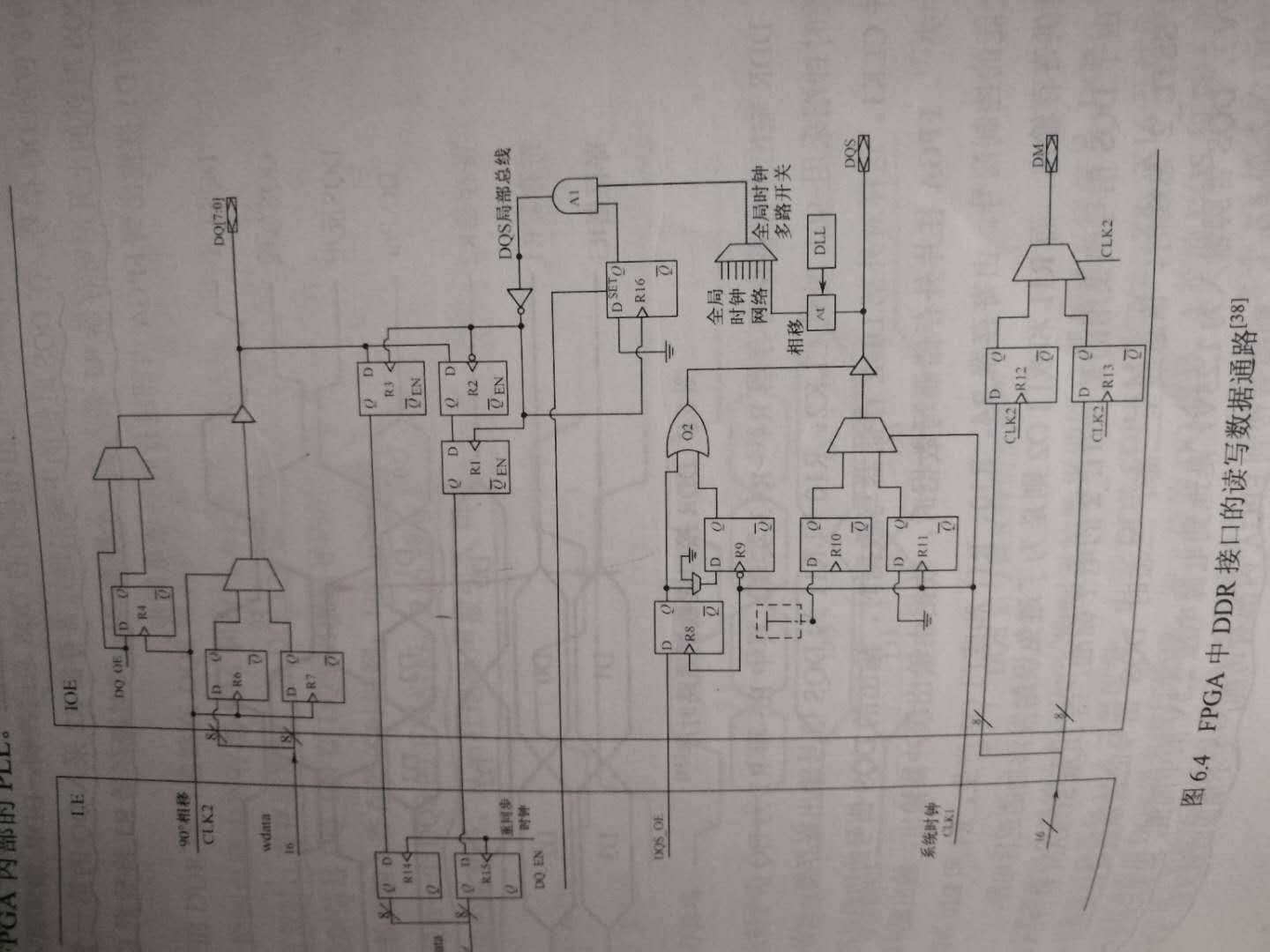

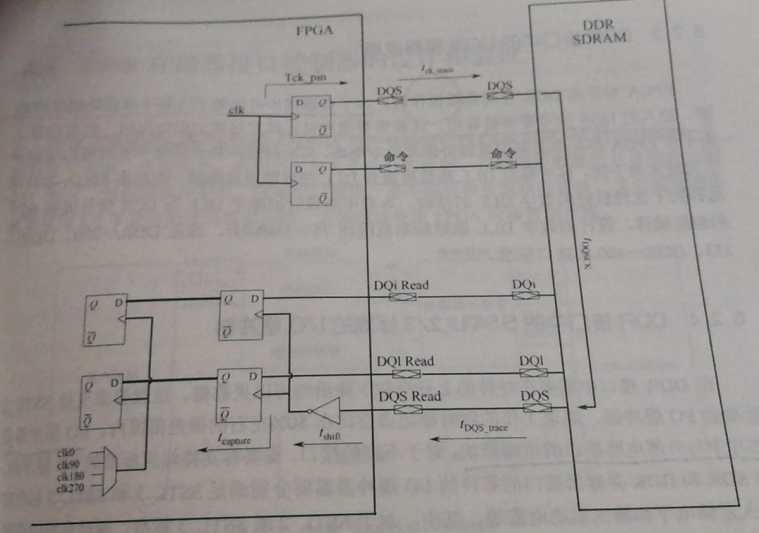

在FPGA芯片中,对读写数据的采样是由数据通路通过操控外部DDR存储器接口来完成的,下图是FPGA中的读写数据通路电路,由读写两部分的寄存器组成,主要实现数据读入和写出的时序逻辑功能。其中CLK1为系统时钟,CLK2为-90°的时钟,他们均来源于FPGA内部的PLL。

当FPGA从外部DDR存储器读数据时,由于从存储器来的数据信号DQ和数据选通信号DQS的边沿是对齐的,为了在DQS的上升沿和下降沿,为了在DQS的上升沿和下降沿均采样数据,需要对信号DQ或DQS移相,而每个DQS信号采样8个DQ,如果对DQ信号进行相移的话,需要8个相移补偿单元,这样开销相对较大,因此选择对DQS进行相移 ,如上图所示,这里设计的数据通路采用一个DLL控制延时链,使DDR SDRAM来的数据选通信号DQS相移90°,再进入DQS局部总线。这样同时达到了节省开销的目的。

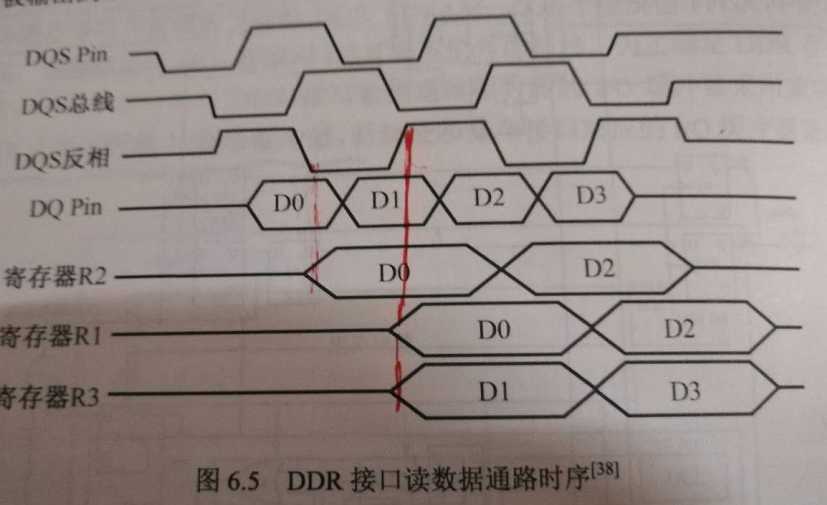

下图为DDR接口读数据通路时序。DQS总线信号在进入DDR输入寄存器之前需要经过反相器反相以确保采样数据的正确性。DDR输入寄存器由下图中的寄存器R1~R3实现。它们的时钟端由相移后的DQS总线控制。DDR输入寄存器的数据端为9位的DQ信号,在DQS时钟的下降沿通过寄存器R2采入DQ的第一个数据D0,在DQS时钟的上升寄存器R3采入第二个数据D1,同时寄存器R1将数据D0同步。数据D0和D1被输出到FPGA内部进行时钟域重同步。

DDR输出寄存器由寄存器R4~R13实现,其中R6和R7为DQ信号输出寄存器,它们的时钟端采用-90°时钟CLK2,;

R10和R11为DQS信号输出寄存器,时钟端采用系统时钟CLK1.这样对外部DDR写数据的时候,输出的DQS信号的边沿对齐到数据DQ的中央。

FPGA往片外存储器写数据时,数据由输出缓冲器输出。输出缓冲器需要有输出使能的控制信号,由寄存器R4、R10、R11和或门O2产生。R4和R10为输出使能信号提供寄存器输出,而R11和或门O2则是为了避免误触发添加的逻辑电路。

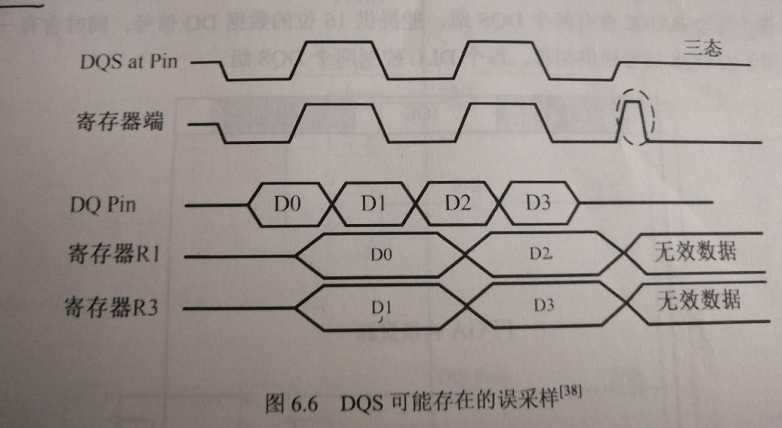

由于DQS信号线采用的SSTL_2的电平标准,当DDR SDRAM和FPGA芯片都不驱动SSTL_2总线时,该总线呈三态。三态时DQS信号的传输线被拉到端接电压Vtt(1.25V),DQS管脚输入为1.25V,是地到电源电压2.5V的中间值。如果此时有轻微的噪声引入到三态的总线上,则信号传到FPGA内部有可能产生不期望的触发沿,导致信号误触发。

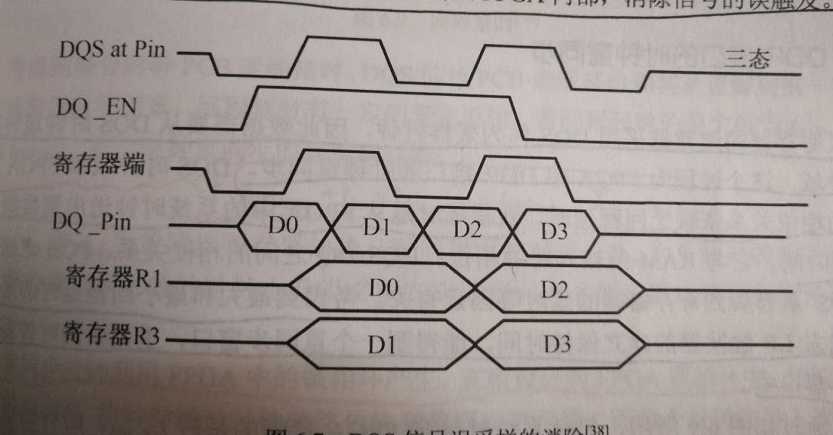

这里设计的DDR接口电路在DQS管脚附近增加了一个逻辑电路,用以消除这种误触发情况。该控制电路由寄存器R16和与门A1组成。R15是一个复位置位寄存器,当DQ_EN信号有效时,寄存器置位,当DQ_EN信号失效且时钟上升沿时,寄存器被复位。

如下图所示,控制吸纳后DQ_EN在DQS出现前导码时有效,R16被置位,此时与门A1导通,DQS信号能传输到输入寄存器的时钟端;DQ_EN在最后一个有效DQS下降沿出现之前失效。这样经过最后一个DQS的下降沿后,R16被复位为低电平,与门A1屏蔽从DQS传来的由于噪声造成的跳变沿。从而杜绝噪声被引入到FPGA内部,消除信号的误触发。

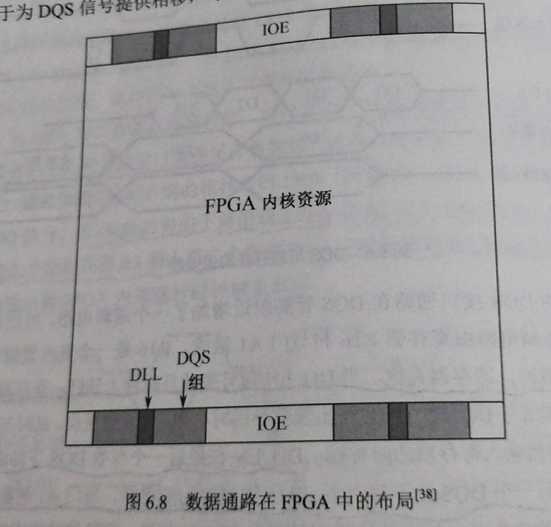

控制器的数据通路主要传送采样信号DQS、数据信号DQ、和数据屏蔽信号DM三类信号。由于DDR SDRAM有X4、X8、X16几种位宽模式,因此数据通路用DQS组来进行管理,把8位的DQ信号、1位的DQS和DM信号作为一个DQS组。根据设计的FPGA资源情况,一共设计了8个X8模式的DQS组分别置于芯片的顶部和底部,分布在FPGA芯片中的IO模块中,其每个BANK含有两个DQS组,能提供16位的数据DQ信号,同时含有一个DLL,用于为DQS提供相移,每个DLL控制两个DQS组。

2.2DDR接口的时钟重同步

输入寄存器的读数据采用DQS作为采样时钟,因此数据需要从DQS时钟域转换到FPGA系统时钟域,这个过程为FPGA中DDR接口的时钟重同步。

DQS时钟域和FPGA系统时钟域的相位关系依赖于回程延时。回程延时是从FPGA中的系统时钟送出到数据到达FPGA的时间。它与RAM的输入时钟相位、DQS/DQ之间的相位关系。PCB走线延时以及DQS从管脚到寄存器端的延时等因素有关。

考虑到最大和最小回程延时的重叠区域,再减去LE触发器的建立保持时间,能得到一个重同步窗口,重同步的时钟需要选择在这个窗口中。

回程延时如下图所示,包括系统时钟到FPGA管脚的延时tck_pin、时钟的板级传输延时tck_trace、DQS的相位偏移tshift和DDR输入寄存器的采样时间tcapture。

总的回程延时tRTD为:

tRTD = tck_pin + tck_trace + TDQS_trace + tDQSCK + tshift + tcapture

考虑到差分时钟PCB走线延时、DQS信号PCB走线延时和其从管脚到第一次采样D触发器的延时等因素,回程延时有一定的变化范围。若回程延时的最大值为tRTDmax,最小值为tRTDmin,那么时钟重同步的有效接口为:

tRTDmax + tsu < tsync_valid < tRTDmin + Tclk – thd

所选择的重同步时钟的时钟上升沿必须在有效窗口内才能正确地使数据同步到系统时钟域中。

重同步时钟利用FPGA中的锁相环产生,在所设计的FPGA锁相环中,使能产生两路相位差为90°的时钟网络传输到重同步寄存器,而每个时钟在进入寄存器前可以编程为反相输入,因此有4路不同相位的时钟可以作为重同步时钟,分别为相对于系统时钟偏移0°、90°、180°、和270°的时钟。当列地址选通潜伏期(CAS Latency,CL)为2或3时,考虑到实际回程时间小于1个时钟周期,重同步最好选择270°相位的时钟,若列地址选通潜伏期为2.5个时钟周期时,则重同步时钟最好选择90°相位的时钟。

2.3DDR接口中的DQS相移电路

FPGA对外部DDR存储器读操作时,为了在源同步时钟的上升和下降沿均能采样数据,输入的DQS信号需要被相移。这就需要通过延迟锁定环锁定固定延时,实现相移。

由于在FPGA芯片中主要的逻辑资源是数字电路,其电源噪声和衬底噪声会对模拟电路产生较大的干扰。这对模拟DLL和数模混合DLL的性能造成影响,因此在FPGA芯片中选择抗干扰较好的数字DLL的结构。

2.4DDR接口中的SSTL_2/3标准的I/O缓冲器

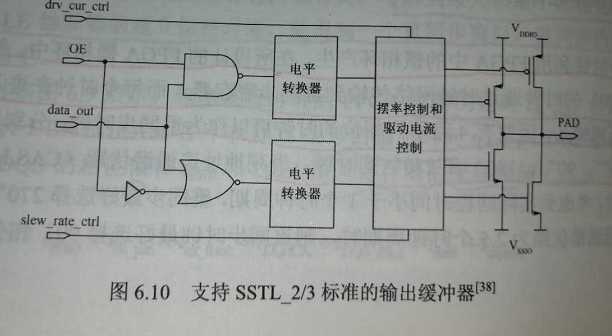

在DDR接口中需要在时钟的上升沿和下降沿均可以采数据。这就要求支持SSTL_2的标准的I/O缓冲器,高速工作的同时输出占空比50%左右的偏差范围内。I/O缓冲器时芯片中与外部电路接口的电路模块。对于不同的接口,需要支持相应标准的I/O缓冲器。

与SDR和 DDR存储器接口的芯片的I/O缓冲器需要分别满足SSTL_3和SSTL_2标准的输入逻辑电平和输出驱动电流等。其中,对于SSTL_2或SSTL_3标准,驱动电流的两种不同规范相应于Class I和Class II的输出缓冲器。

下图是带摆率控制和驱动电流控制的支持SSTL_2/3标准ClassI和Class II的输出缓冲器。电平转换器实现信号高电平由芯核电源电压变为I/O电源电压。

3、DDR存储器接口控制器的设计和验证

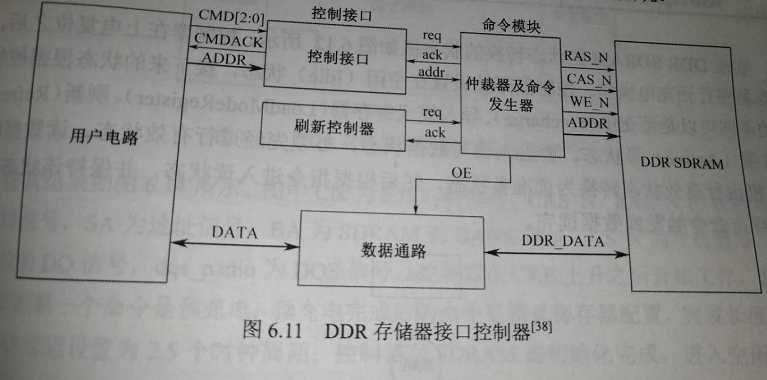

DDR存储器控制器的作用是为FPGA用户电路提供对DDR SDRAM的访问控制,包括对读写请求、地址信号、数据信号和命令信号的控制。存储器控制器的总体结构如下图所示,包括刷新控制器、控制接口模块、命令模块和数据通路模块。其中数据通路模块采样上一节所说的读写数据通路,其他模块使用FPGA内核资源实现。

3.1控制器的刷新模块

**刷新请求命令有限与控制接口来的命令。**如果控制接口的命令和刷新请求命令同时到达,则控制仲裁器会延后送出控制接口的命令。DDR SDRAM存储体中的每一行在间隔64ms内必须对其进行刷新,刷新命令对一行刷新,因此发送间隔由SDRAM的总行数决定。在刷新控制模块中设计了一个刷新计数器,每当刷新控制器计数满时发送一个刷新命令。

3.2控制器的命令和状态转换

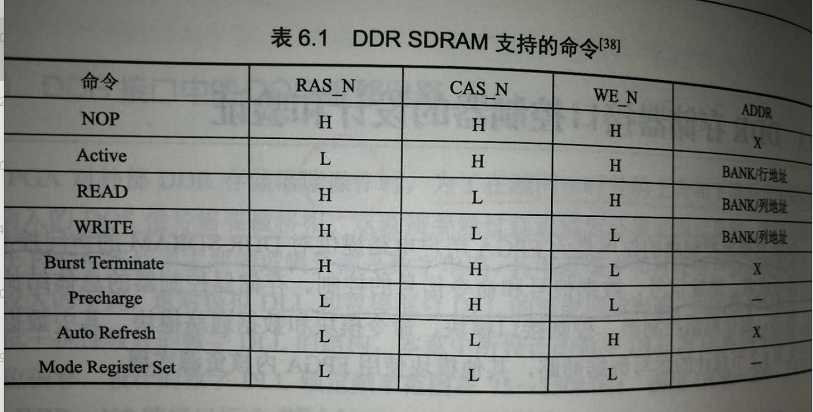

SDRAM支持的命令包括:空操作(NOP)、激活操作(Active)、突发读(Burst Read)、突发写(Burst Write)、自动刷新(Auto Refresh)、预充电(Precharge)和模式寄存器配置(Mode Register Set)。这些命令由命令接口CAS_N、RAS_N和WE_N送到DDR SDRAM中,其基本操作命令如下表:

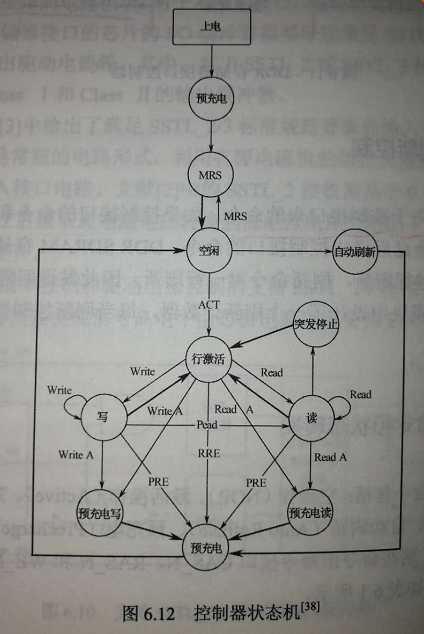

实现DDR SDRAM的状态转换的状态机如下图所示。控制器在上电复位之后,对存储器进行预充电操作。控制器开始设置在空闲(IDLE)状态,接下来的状态根据控制命令的不同可以是预充电(Precharge),导入模式寄存器(LoadModeRegister)、刷新(Prefresh)、行有效(Active)等状态。要进入读写数据状态,必须先经过行有效状态。读数据时,状态机由行有效装换我读准备状态,然后根据指令进入读状态,并保持该状态直到脉冲终止命令触发或数据读完。

3.3验证结果与分析

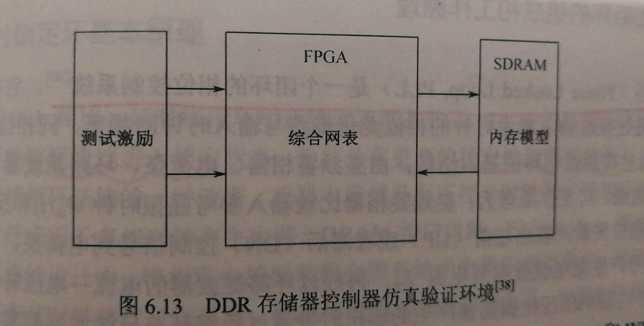

对DDR存储器控制器进行仿真验证,仿真环境如下图所示。其中DDR存储器控制器的设计通过FPGA芯片和配套的软件综合成网表文件,DDR SDRAM选用64MB的MT46V16M8的verilog模型。

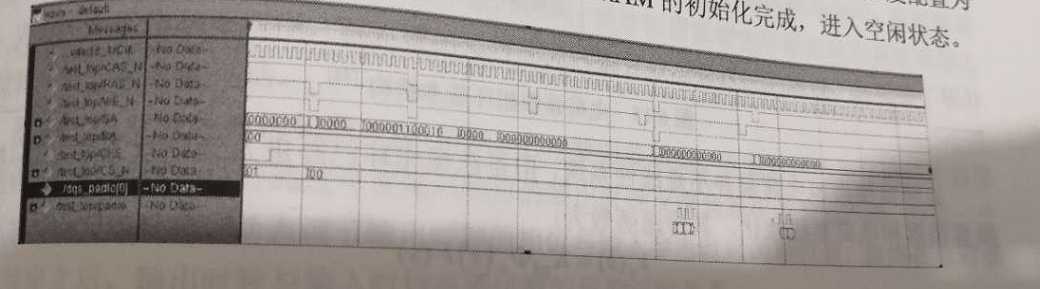

图中Clk为系统时钟信号,CAS_N,RAS_N和WE_N是命令接口信号,SA为地址信号,BA为SDRAM的bank地址,CS_N为片选信号,padio为8位的DQ信号,dqs_padio为DQS信号。控制器在CKE上升之后开始工作,在CKE上升后的第一个命令是预充电;预充电完成后的命令是寄存器配置,突发长度设置为4,CAS延迟设置为2.5个时钟周期;控制器对SDRAM的初始化完成,进入空闲状态。

接着控制进入写数据状态,在发送WRITE命令之前先激活相应的行地址。在发送WRITE命令的2个时钟周期后,控制器往dqs_padio和padio输出采样信号和数据信号。

控制器在读命令READ之前需要发送一个激活操作Active命令;在READ结束后2.5个时钟周期胡读数据出现在DQS和DQ总线上。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://yundeesoft.com/24543.html