大家好,欢迎来到IT知识分享网。

原文来自知乎,侵删

本文试图阐述开关电源设计与测试中的若干细节问题,这是一些比较容易被忽视的小细节。

一、纹波的测量

(一)、纹波的组成成分

电源性能的最直观的表现是电源纹波,所谓电源的纹波就是指电源输出电压的波动。

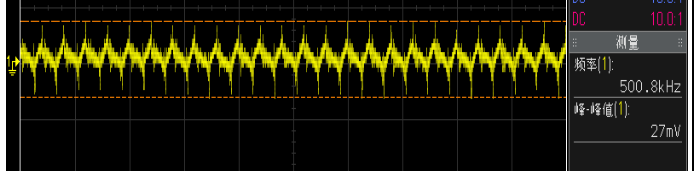

如果是开关电源,输出纹波是有规律的摆动,摆动的频率等于开关频率。纹波的形成是因为电流流过输出电容在电容的ESR上所引起的压降,开关电源中不断地有脉动的电流流经电容,所以它的纹波的频率等于开关频率。

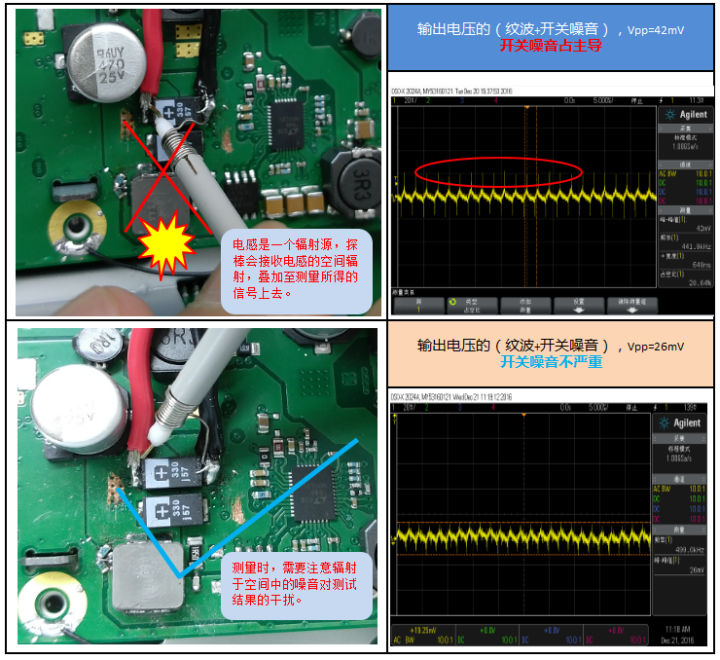

图1、开关频率为500KHZ的开关电源的输出纹波

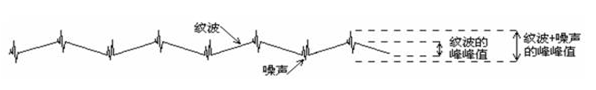

然后,细心的你还会发现,脉动的电压波动上叠加了细细的“针针”,这是开关电源开关信号所引起的开关噪音。因此,准确地说,电源的输出波动实际上有两个部分组成,纹波与噪音。

图2、电源的输出波动的分解

前面已提及纹波的形成是因为脉动的电流流过输出电容,然后在电容的ESR上所形成的压降,所以要想消灭纹波是不可能的,只能是尽可能地去减小。

而叠加在纹波上的噪音却是有机会得到改善的,在开关电源中,开关管引起的开关噪音会叠加到输出电压上,然后因为其频率很多,很难被滤波器滤除,所以容易扩散至整个PCB板子,引起EMC问题。

关于开关噪音的改善,下文再详细阐述。在想办法解决问题之前,我们需要获得准确的信息来作决策的依据,错误的信息输入必将得到更加错误的决定。

(二)、如何正确地测量电源的输出电压的纹波?

为了叙述的方便,我们一般把输出电压的波动统称为纹波,但是我们在内心深处必须时刻有一个根深蒂固的概念,我们在测试时实际上是为了获取两个信息:纹波电压以及噪音。

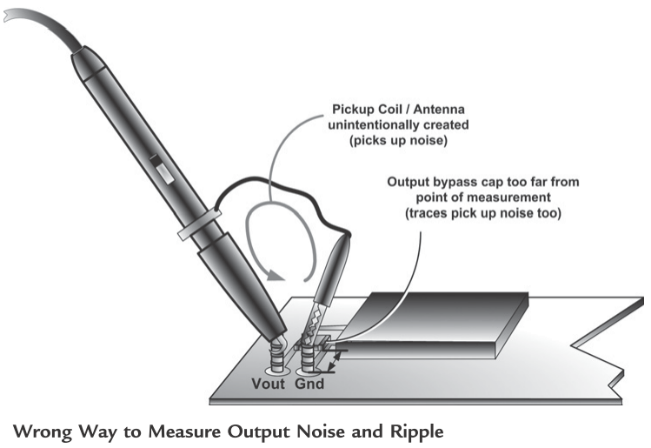

纹波电压的形成与脉动电流和电容的ESR相关,所以在测试时需要分别测试不同负载电流下的纹波电压,这是基于不同的脉动电流的考量。最需要的注意的是不要人为地增加ESR,所以测试时需要在输出电容的两端就近测量,否则路径会额外增加ESR值。

噪音的形成与开关路径上的寄生电感相关,所以在测试时需要注意不能引进额外的寄生电感,否则测试所得的开关噪音会大于实际值。

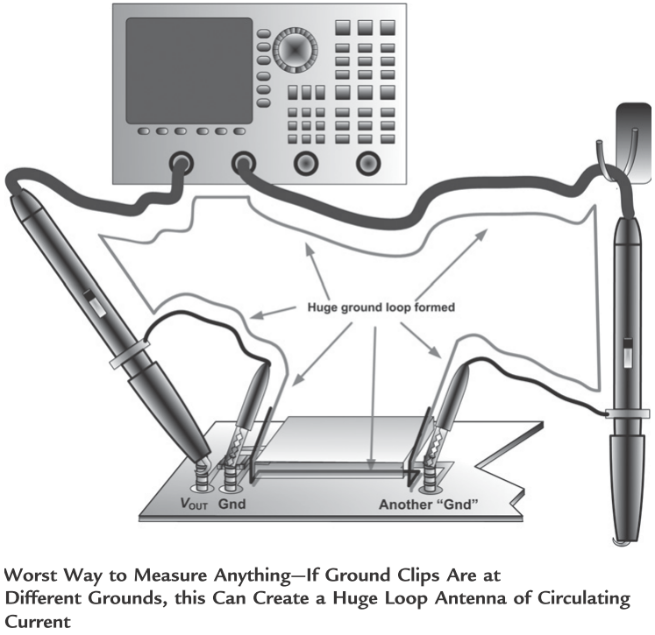

图3和图4是两种错误的纹波测量的方法,它们正确的地方是在电容两端就近测量,错误在于引入或者说吸收了噪音,使得测试所得的结果偏离实际情况。

图3、错误的纹波测量方法

图4的错误很容易被忽视,就是在测试时必须移除多余闲置的探棒,避免人为地引入噪音。

图4、在纹波测量时,请移除多余的闲置探棒

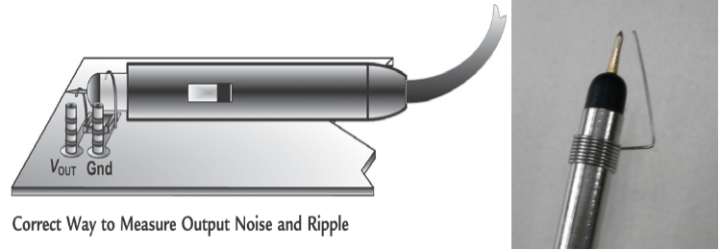

图5、正确的纹波测量方法

正确测量纹波的姿态是使用纹波帽,如图5示意,这样可以保证测量路径最短,引入的噪音最少。

图6、简易高效的纹波测量方法

如果,手头条件有限,没有纹波帽咋办?其实很简单,可以自制。在密集测量时,还可以使用图6的方法,将自制的纹波帽直接焊到PCB板上。

(三)、如何优雅地测量电源的输出电压的纹波?

前文讲了如何正确地测量纹波,为什么要这么做,这样做的原理是什么,等等。很多事情算是老生常谈了,相信多数人是知道的并且很熟悉的。

在这里,我想再提一个概念,优雅地测试。前面是谈如何正确地测量。正确测量是一个技术问题,有具体的操作步骤和规范,而优雅是一个态度问题,很多时候你会发现两个不同的人基于同样的仪器和操作手册却得到了不同的测量结果。

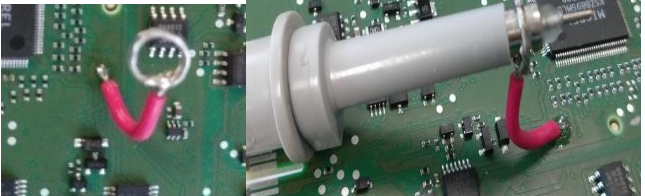

图7是测试人员在测试纹波时,探棒没有“站直”,斜躺着,结果很不幸躺到了电感上,而电感是辐射源。在质疑其测量结果时,他还委屈,说采用了纹波帽,而且是就近测量的啊。后来,仔细观察方才发现测量的姿势有问题。

图7、不同的测量姿势,得到不同的结果

(四)、如何评估测量结果的正确性?

看了前文的叙述,你也许会很紧张,如何才能保证每一个测试的姿势都是非常之优雅呢?是否每一项测试都需要亲力亲为呢?

其实是有很多小窍门去判断测试结果是否可信的,在电源的测试中,会有很多小的子项目的测试,子项目之间实际上有关联的,细心的你定能“火眼金睛”的看出报告里的猫腻。

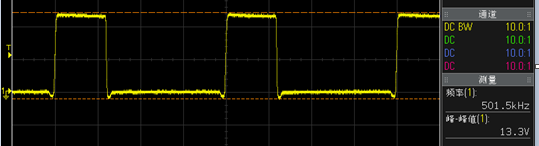

继续前文图7的测试结果,开关噪音因为没有被滤波器滤除有残留,残留被叠加到输出电压上形成噪音。所以,往前追溯很容易找到噪音的源头,而图7的测试报告里,发现由开关管输入到电感的开关节点的电压信号的过冲和下冲算是比较好的(如图8),不可能造成那么大的输出噪音,这是理直气壮地质疑测试方法有问题的根据。

图8、BUCK电路中,MOSFET与电感之间的开关节点(V_PHASE)的电压波形

如果你是一位测试人员,在测试时需要做好自检的工作,避免后续不必要的返工,以下思路供参考。

电感是一个很强的辐射源,开关噪音不但通过传导也会以空间辐射的形式,往外散发。为了避免空间中辐射的噪音对测结果的误导,可有以下两个对策来应对。

1)、在测试时,探棒可尝试不同的姿势,选择一个空间辐射对测试结果影响最小的姿势。

2)、对测试结果的交叉验证可以减少错误结果发生。输出电压上的开关噪音,实际上和V_PHASE是有对应关系的。

V_PHASE的边沿振铃一般难以被输出滤波器处理掉,最终表现为输出电压上的开关噪音。如果输出电压上的开关噪音很大,但是V_PHASE的边沿振铃却不明显,则说明你所测试到的噪音很可能是来自空间中的辐射,此时可动一动探棒与PCB板子的夹角,努力将接收到的空间辐射降低到最小。

二、 电源噪音的处理

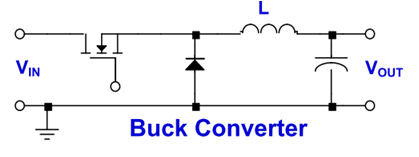

前文详细阐述了纹波的组成、纹波及噪音的产生机理、如何正确地测量纹波、如何交叉验证测试结果确保报告的可靠性等等。测试是为了发现问题,预警风险,包括已知的以及潜在的。如果是光测试而不解决问题等于是耍流氓。接下来,我们来谈一谈如何解决纹波相关的问题,以BUCK电路为例。

图9、BUCK的原理模型

开关电源的LC滤波器几乎是没有降低纹波分量的能力的,因为纹波是脉动电流流过输出电容,在电容的ESR上引起的压降。所以,如果需要降低纹波电压,就需要降低电容的ESR,可以选用LOW ESR的电容,也可以多个电容并联来降低ESR。但是凡事都不是绝对的,如果纹波电压已经可以符合负载的需求了,就不要去追求完美了,特别是使用叠加电容的手段来降低纹波,过大的输出电容是有副作用的。

开关电源的LC滤波器对开关转换时产生的边沿噪音更是无能为力,开关噪音会产生更高频的谐波,最大的恶果是对EMC性能造成负面影响。

开关噪音与开关波形V_PHASE的上升/下降时间以及路径上的寄生电感息息相关,寄生电感的改善比较麻烦,与Layout设计相关,也和芯片的内部设计及性能相关。一般比较常采用的方法是降低开关信号的上升与下降时间,这样做的副作用是增加了开关过程中的交越导通损耗,在一定程度上降低了电源的效率。

所以,优化输出纹波及噪音性能实际上是在寻找一个平衡点,我们需要有全局意识,切不可为了某一个单项的指标而“不折手段”。

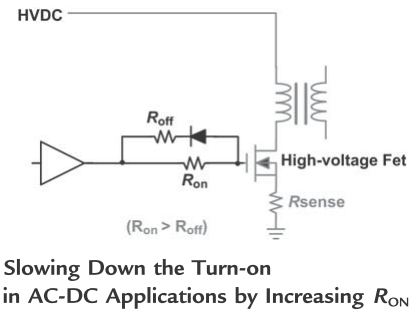

1)、 MOSFET外置的开关斜率调整

图10、MOSFET外置,栅极串联电阻调整开关斜率

如果开关电源的MOSFET是外置的,可尝试用一个小电阻与栅极串联,但这对开通和关断电压均有影响,如果MOSFET的关闭时间过长,则有上下管直通的风险。

因此,一般的原则是“打开慢一些,电流变化就会缓一些,由寄生电感产生的振铃也就会小一些;关闭的时候利索一些,不能让另一侧的管子等待太久”。如果打开与关闭的斜率无法协调,不妨尝试配置不同的栅极电阻,然后使用二极管进行隔离,如图11。

图11、MOSFET外置,栅极串联电阻分别调整上升与下降斜率

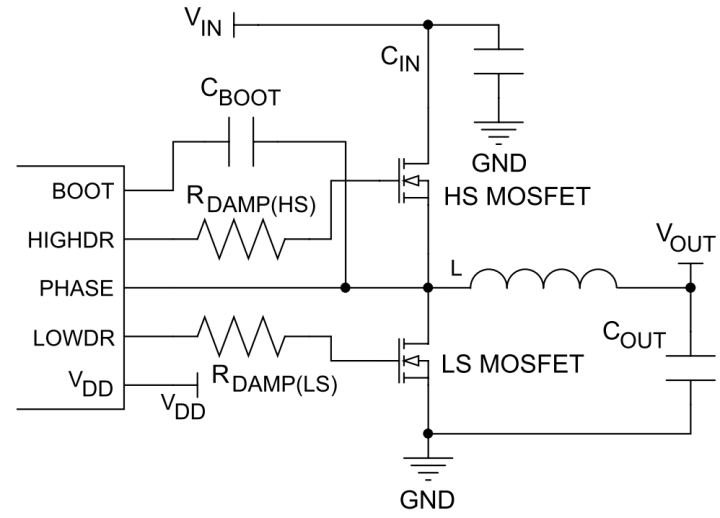

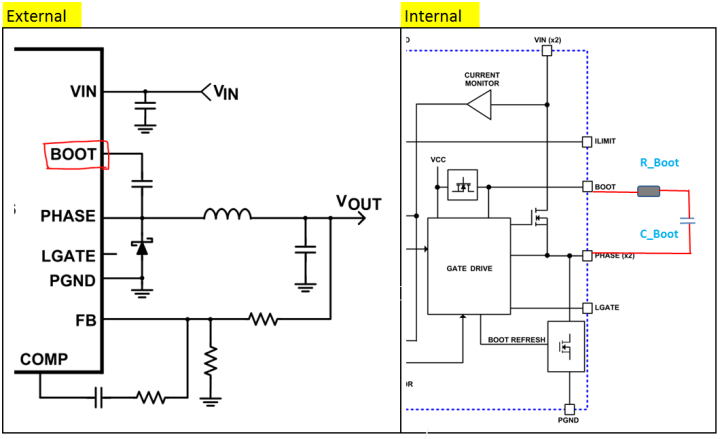

2)、MOSFET内置的开关斜率调整

集成度高的DC-DC变换器已将MOSFET集成,所以我们无法通过栅极串电阻的方式来减缓开关斜率。在这种情况,如果上管是N-MOSFET的话,芯片会有一个ChargePump的管脚(BOOT)。可以使用一个小电阻(通常为10~20欧姆)与驱动级(BOOT)的耦合电容串联,这在一定程度上可以减缓开关的斜率,如图12所示。

图12、MOSFET集成,BOOT管脚串联电阻调整开关斜率

3)、开关噪音的吸收

在设计中建议预留缓冲电路(Snubber)的位置,Snubber与下管MOSFET或者续流二极管并联。

- 在Layout设计时,snubber电路需与下管MOSFET或续流二极管紧贴,避免过孔;

- Snubber一般由R和C组合而成,可将电阻R放置于和地相连的那端,有助于散热。

Snubber设计无明确的计算公式,因为板子的寄生参数及环境千差万别,所以基本上是靠实际调试和逐步逼近。以下调试的套路,仅供参考:

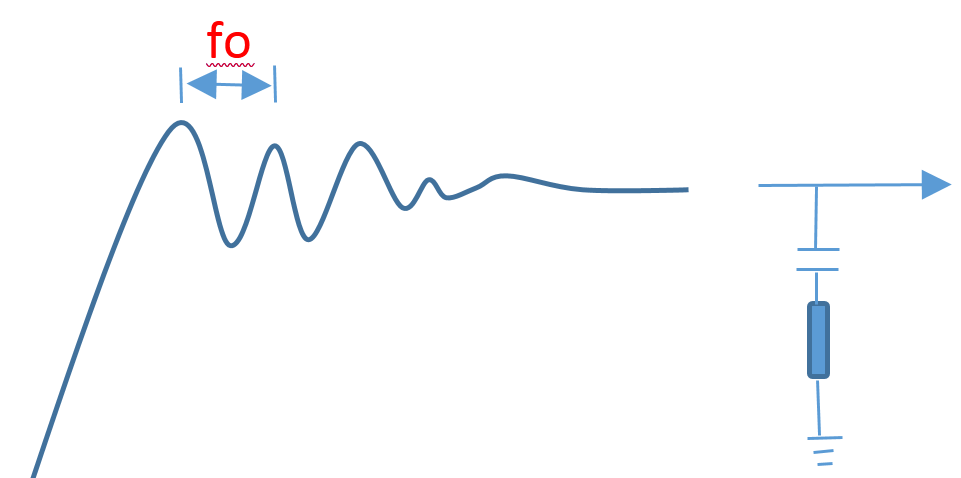

图13、Snubber的调试

1、测量未接Snubber电路时的振荡信号周期(1/fo);

2、将高频电容(Co)跨接在要吸收的器件上,确定电容的值,减缓振荡使周期是原来周期的三倍;

3、确定电容之后,与电容串联的电阻可用以下公式大约估算:

有很多R和C的组合可以产生满意的波形,但上述R和C的选值应该产生最小的损耗和最有效的效果。同时,避免Snubber电路对开关波形的损伤。

4)、拦截开关噪音

不管采用何种措施,开关噪音终究是无法回避的。为了减小系统的整体噪音,不得不采用围追堵截的措施。

首先,在电源的“入口”阻挡(比如安放一粒100nF的旁路电容);

然后,在电源系统的内部尽量减弱噪音(减缓开关斜率、安装Snubber电路、减小寄生参数等);

最后在“出口”处,尽可能做好拦截(增加LC或Bead-C滤波器)。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://yundeesoft.com/14909.html