大家好,欢迎来到IT知识分享网。

概述

过采样就是对输入信号进行采样,采样频率是输入信号最高频率的2倍以上。

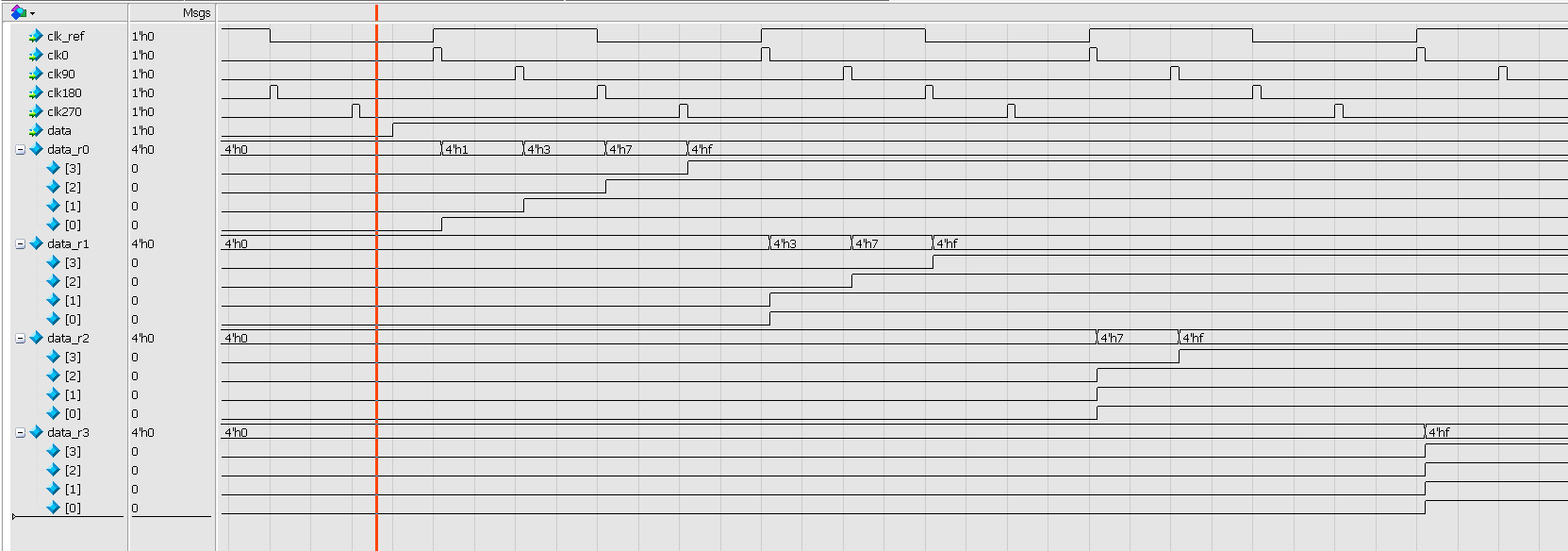

fpga在1个clk0周期内对 输入信号data 进行4次采样;分别在clk的0度、90度、180度、270度位置进行采样,

4个周期后在clk0时钟域输出采样到的并行数据;

为什么第4行第1个触发器用clk270时钟?

因为:

第1拍先实现270度位置采样;

第2拍再将270度采样后的数据,180度位置采样,(0.75的建立时间+0.25的保持时间);

第3拍再将180度位置采样后的数据,90度位置采样,(0.75的建立时间+0.25的保持时间);

第4拍将90度位置采样后的数据,0度位置采样,(0.75的建立时间+0.25的保持时间);

tb

reg clk_ref=1 ;

reg clk0 =0 ;

reg clk90 =0 ;

reg clk180 =0 ;

reg clk270 =0 ;

reg data ;

initial begin

forever begin clk_ref =#20 ~clk_ref;end

end

initial begin

forever begin @(posedge clk_ref); clk0 =1;#1;clk0 =0; end

end

initial begin

#10;

forever begin @(posedge clk_ref); #10; clk90 =1;#1;clk90 =0; end

end

initial begin

#20;

forever begin @(posedge clk_ref); #20; clk180 =1;#1;clk180 =0; end

end

initial begin

#30;

forever begin @(posedge clk_ref); #30; clk270 =1;#1;clk270 =0; end

end

initial begin

data=0;

#200;

@(posedge clk270);#5;

data=1;

#200;

data=0;

#200;

$stop();

end

cdr u0_cdr(

.clk_ref (clk_ref ),//input clk0 ,

.clk0 (clk0 ),//input clk0 ,

.clk90 (clk90 ),//input clk90 ,

.clk180(clk180 ),//input clk180 ,

.clk270(clk270 ),//input clk270 ,

.data (data ) //input data

);

main

`timescale 1ns/100ps

module cdr(

input clk_ref ,

input clk0 ,

input clk90 ,

input clk180 ,

input clk270 ,

input data

);

reg [3:0] data_r0=0 ;//1级延时

reg [3:0] data_r1=0 ;//2级延时

reg [3:0] data_r2=0 ;//3级延时

reg [3:0] data_r3=0 ;//4级延时

//data_r0

always@(posedge clk0 ) data_r0[0]<= #1 data ;

always@(posedge clk90 ) data_r0[1]<= #1 data ;

always@(posedge clk180) data_r0[2]<= #1 data ;

always@(posedge clk270) data_r0[3]<= #1 data ;

// data_r1

always@(posedge clk0 ) data_r1[0]<= #1 data_r0[0] ;

always@(posedge clk0 ) data_r1[1]<= #1 data_r0[1] ;

always@(posedge clk90 ) data_r1[2]<= #1 data_r0[2] ;

always@(posedge clk180) data_r1[3]<= #1 data_r0[3] ;

// data_r2

always@(posedge clk0 ) data_r2[0]<= #1 data_r1[0] ;

always@(posedge clk0 ) data_r2[1]<= #1 data_r1[1] ;

always@(posedge clk0 ) data_r2[2]<= #1 data_r1[2] ;

always@(posedge clk90 ) data_r2[3]<= #1 data_r1[3] ;

// data_r3

always@(posedge clk0 ) data_r3[0]<= #1 data_r2[0] ;

always@(posedge clk0 ) data_r3[1]<= #1 data_r2[1] ;

always@(posedge clk0 ) data_r3[2]<= #1 data_r2[2] ;

always@(posedge clk0 ) data_r3[3]<= #1 data_r2[3] ;

endmodule

波形图

参考

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://yundeesoft.com/15057.html