大家好,欢迎来到IT知识分享网。

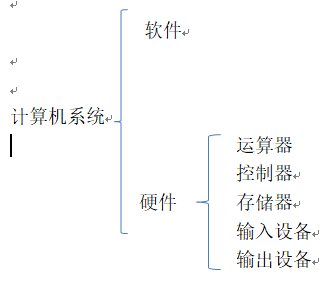

一、计算机的组成

运算器和控制器等组成CPU ,CUP是硬件的核心,用于数据的加工处理,能完成各种算数、逻辑运算及控制功能。存储器分为内存和外存,输入设备和输出设备合称外设。

CPU负责获取程序指令,对指令进行译码并执行。功能包括:程序控制、操作控制、时间控制、数据处理以及对系统内部和外部的中断做出 相应和相应的处理。

CPU主要由运算器、控制器、寄存器组和内部总线等部件组成。

运算器由算数逻辑单元(ALU)、累加寄存器(AC)、数据缓冲寄存器(DR)和状态条件寄存器(PSW)等组成,它是数据加工处理部件,完成计算机的算数和逻辑计算。运算器是执行单元,接收控制器的命令进行动作。

控制器由程序计数器(PC)、指令寄存器(IR)、指令译码器、时序产生器和操作控制器组成,它控制整个CPU工作,保证程序正确执行且处理异常。控制器包括指令控制逻辑、 时序控制逻辑、总线控制逻辑和中断控制逻辑等几个部分。指令控制逻辑完成取指令、分析指令和执行指令的操作;时序控制逻辑为每条指令按时间 顺序提供应有的 控制信号;总线逻辑是为多个功能部件服务的信息通路的控制电路;中断控制逻辑用于控制各种中断请求并根据优先级进行排队,逐个交给CPU处理。

寄存器可分为专用寄存器和通用寄存器。运算器和控制器间的是专用寄存器,作用是固定的。

多核CPU即在一个单芯片上继承两个甚至多个处理器内核,CPU所有计算,接收/存储命令、处理数据都由内核完成。多核的主要优点是满足用户同时进行多任务处理的要求。

二、 进制转换

R转10进制 :按权展开法 R的k次方求和 (k…… 3 2 1 0 . -1 -2)

10转R:短除法 除以R 记住余数 余数逆序排上去

10 进制小数转: 主要是小数部分乘以2,取整数部分依次从左往右放在小数点后,直至小数点后为0。

Eg:0.125: 0.125*2 = 0.25 整数部分0 再将小数部分0.25乘以2,得0.5,然后取整数部分0 再将小数部分0.5乘以2,得1,然后取整数部分1 直到小数部分全为0 整数部分顺序排列 得到结果 0.001

三、数据表示

数值在计算机中的表示的形式称为机器数,特点是二进制计数制,机器数对应的实际数称为数的真值。机器数有无符号数和 带符号数之分。带符号的数可用原码、反码、补码和移码等编码方式(码制)表示。

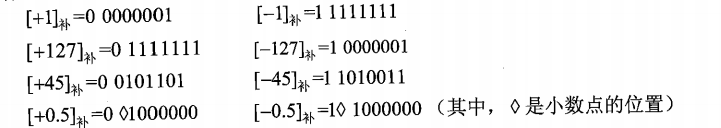

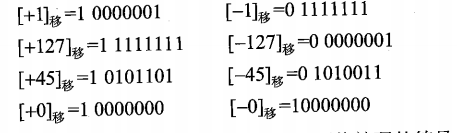

(1)原码、反码、补码和移码

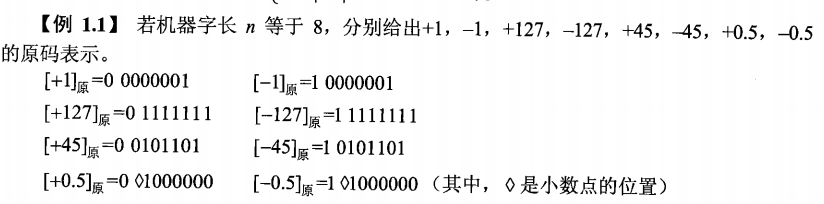

原码符号位 +:0 -:1 -127到+127

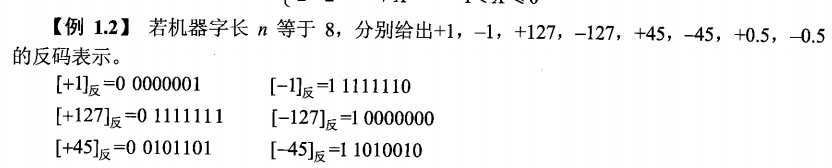

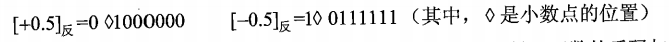

反码 正数:正数的反码与原码相同、负数:最高位不变,其他按位取反 -127到+127

补码 正数:补码与原码相同 负数:补码=反码+1 -128到127

移码(用来做浮点运算中的阶码) 补码的首位(最高位)取反

(2)定点数和浮点数

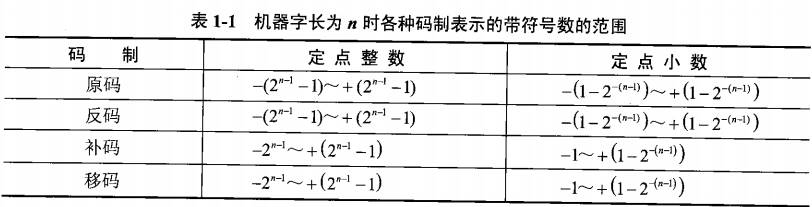

定点数是小数点固定的数,浮点数是小数点位置不固定的数,浮点数可以表示范围更大的数。

定点数包括定点整数和定点小数,范围如下表:(原码和反码中0占用了两个编码)

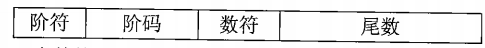

二进制数中,N可以表示为

IEEE754中规定:

1、单精度浮点数字长32位,尾数长度23,指数长度8,指数偏移量127;双精度浮点数字长64位,尾数长度52,指数长度11,指数偏移量1023;

2、约定小数点左边隐含有一位,通常这位数是1,所以上述单精度尾数长度实际为24(默认省略小数点左边的1则为23),双精度尾数长度实际为53(默认省略小数点左边的1则问53);

举例:利用IEEE754标准将数176.0625表示为单精度浮点数。

解:

第一步:将10进制转换为2进制

(176.0625)10 = (1011 0000.0001)2

第二步:对二进制数进行 规格化处理

1011 0000.0001 = 1.011 0000 0001 * 2^7

第三步:去掉b0并扩展为单精度规定的23位尾数

011 0000 0001 0000 0000 0000

第四步: 求阶码

E = 7 + 127 = 134

(134)10 = (1000 0110)2

所以,176.0625的单精度 浮点数表示形式:0 1000 0110 011 0000 0001 0000 0000 0000

浮点数运算:对阶 –> 尾数计算 –> 结果格式化并判溢出 –>舍入处理 –>溢出判别

(四)校验码

使用校验码来检测传送的数据是否出错。基本思想:数据可能的编码有两种:合法编码和错误编码。合理的设计错误编码和编码规则使得数据在传送过程 中出现某种错误时会变成错误编码,从而检测接收到的数据是否错误。

码距指编码系统中任意两个合法编码之间 至少有多少个二进制位不同。

有三种校验码:奇偶校验码、海明码、循环冗余校验码。

奇偶校验码通过在编码中添加一个校验位使编码中1的个数为奇数(奇校验)或偶数(偶校验),从而使码距变为2。 后常见奇偶校验码有三种:水平奇偶 校验码、垂直奇偶校验码和水平垂直校验码。

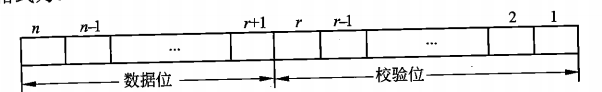

海明码是一种利用奇偶性来检错和纠错的校验方法。在数据位之间的特定位置上插入k个校验码,通过扩大码距来实现检错和纠错。

循环冗余校验码(CRC)利用生成多项式为k个数据位产生r个校验位来进行编码,其编码长度为k+r。代码格式为:

(五)计算机体系结构

1、分类

按处理机的数量分类: 单处理机系统、并行处理与多处理系统和分布式处理系统。

按并行程度分类:Flynn分类法、冯泽云分类法、Handler分类法和Kuck分类法。

Flynn分类法:按指令流(机器执行的指令序列)和 数据流(指令调用的数据序列)的多少进行分类。计算机系统分为单指令流单数据流(SISD)、单指令流多数据流(SIMD)、多指令流单数据流(MISD)和多指令流多数据流(MIMD)。

冯泽云分类法:按并行度对计算机系统分类。最大并行度PM 指计算机系统在单位时间内能处理的最大二进制位数。计算机系统分为字串行位串行(WSBS)计算机、字并行位串行(WPBS)计算机、字串行位并行(WSBP)计算机和字并行位并行(WPBP)计算机。

Handler分类法:基于硬件并行程度计算并行度的方法。计算机硬件结构 分为3个层次:处理机级、处理机中的算数逻辑单元级和算数逻辑单元中的逻辑门电路级。分别计算三级中可以并行或流水处理的程序,计算某系统的并行度。

Kuck分类法:用指令流和执行流及其多重性来描述计算机系统控制结构的特征。系统结构分为: 单指令流 单执行流(SISE)、单指令流 多执行流(SIME)、多指令流单执行流(MISE)和多指令流多 执行流(MIME)。

2、指令系统

一个处理机支持的指令和指令的字节级编码称为其指令集体系结构(ISA)。

ISA分类:从体系结构观点分类:堆栈、累加器和寄存器组。

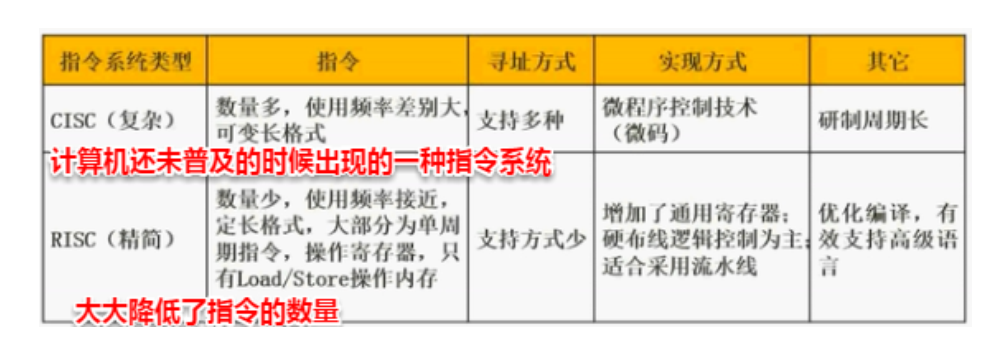

CISC(复杂指令集计算机)和RISC(精简指令集计算机)是指令集发展的两种途径。

指令的控制方式包括:顺序方式、重叠方式和流水方式。

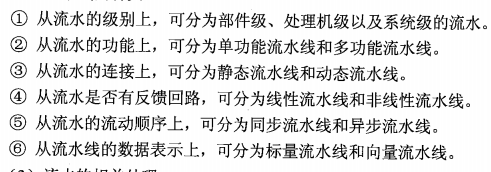

流水线的种类:

流水时多条指令可能对同一主存单元或同一寄存器的“先写后读”的要求, 这就出现了相关。指令相关、访存操作数相关以及通用寄存器组相关等,以上均为局部性相关,解决方法:推后法和通路法。执行转移指令(尤其是条件指令)时可能会改动指令缓冲器中预取到的指令内容,从而造成流水线吞吐率和效率下降,称为全局性相关,解决方法:猜测转移分支、加快和提前形成条件码、加快短循环程序的处理。

RISC中采用的 流水技术有3种:超流水线(时间换取空间)、 超标量(空间换取时间)以及超长指令字。

吞吐率指单位时间内流水线处理机流出的结果数。对指令而言就是单位时间内执行的指令数。if流水线的子过程所用的时间不一样,吞吐率P是最长子过程的倒数:

3、阵列处理机、并行处理机和多处理机

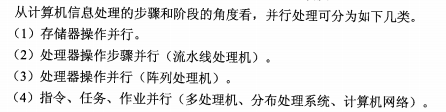

并行性包括同时性(同一时刻)和并发性(同一时间间隔内)。

1)阵列处理机

阵列处理机将重复设置的多个处理单元(PU)按一定的方式连成 阵列,在 单个控制部件(CU)控制下,对分配给自己的数据进行处理,并行地完成一条指令所规定的操作。这是一种单指令流多数据流计算机,通过资源重复实现并行性。

2)并行处理机

SIMD和MIMD是典型的并行计算机,SISD有共享存储器和分布存储器两种形式。

3)多处理机

多处理机由多台处理机组成的系统,每台处理机有属于自己的控制部件,可以执行独立的程序,共享一个主存储器和所有的外部设备。它是多指令流多数据流计算机。

4)其他计算机

集群计算机是一种 并行或分布式处理系统,由很多 连在一起的独立的计算机组成,协同工作,主要解决大型计算问题。

4、存储系统

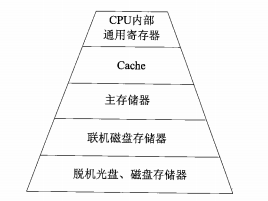

存储系统的层次结构如下图:

存储器的分类:1)按存储器位置:内存(容量小速度快)和外存;2)按存储器材料:磁盘存储器、半导体存储器和光存储器。3)按存储器的工作方式:读写存储器(RAM)和只读存储器(根据数据的写入方式,可分为只读存储器(ROM)、可编程的只读存储器(PROM)、可擦除可编程的只读存储器(EPROM)、电擦除可编程的只读存储器(EEPROM)和闪速存储器)。4)按访问方式分类:按地址访问的存储器和按内容访问的存储器。5)按寻址方式:随机存储器(RAM)、顺序存储器(SAM)和直接存储器(DAM)。

相连存储器:它是按内容访问的存储器.适合于信息的检索和更新。

CPU工作时,送出的是 主存单元的地址,而应从Cache存储器中读写信息。这就需要将主存地址转换成 Cache存储器的地址,这种地址的转换称为地址映像。Cache地址映像有3种方法:直接映像(主存的块与Cache块的对应关系是固定的)、全相联映像(主存的任一块可以调入Cache存储器的任何一个块的空间中)、组相联映像(将Cache中的块再分组,组采用直接映像方式块采用全相联映像)

为使Cache获得尽可能高 的命中率,应使用合适的替换算法。常用算法如下:随机替换算法、先进先出算法、近期最少使用算法、优化替换算法。

现代系统提供一种对主存的抽象,称为虚拟存储,使用虚拟地址 来访问主存, 使用专门的MMU将虚拟地址转换为物理地址后访问主存。虚拟存储器实际上是一种逻辑存储器,实质上是对物理存储设备进行逻辑化的处理。

外存储器用来存放暂时不用的程序和数据,并且以文件的形式存储。主要由磁表面存储器、 光盘存储器及固态硬盘构成。

磁盘阵列是由多台磁盘存储器组成的一个快速、大容量、高可靠的外存子系统,现常见 磁盘阵列 称为廉价冗余磁盘阵列(RAID)

5、输入输出技术(4种)

微型计算机系统中常见内存与接口地址的编制方法有:内存与接口地址独立编制(指令易使用和辨认但数量少功能弱)和内存与接口地址统一编制(增强对接口的操作功能且不再区分内存和接口指令但会导致内存地址不连续)。

直接程序控制(外设数据的输入/输出过程是在CPU执行程序的控制下完成的) 分为无条件传送(外设无条件接受CPU发来的输出数据/向CPU提供输入数据)和程序查询方式(通过CPU执行程序查询外设的状态,判断外设是否准备好接收数据或向CPU输入数据—–缺:降低CPU效率以及无法对外部的突发事件做出实时响应)。

鉴于程序控制I/O使 整个系统性能严重下降,引入中断方式。

中断方式: 系统与外设交换数据时,CPU去处理其他任务,当I/O系统准备好后,发出中断请求信号通知CPU。CPU接到信号完成与I/O系统的数据交换,然后返回被打断的程序继续执行。中断处理方法有多中断信号线法、中断软件查询法、菊花链法、总线仲裁法和中断向量表法。

以上三种方式都需要CPU通过执行程序来实现, 限制了数据的传送速度。

直接内存存取(DMA):数据在内存与I/O设备间直接成块传送,即内存与I/O设备间传送一个数据块的过程中,不需要CPU的干涉,只需要CPU负责开始和 结束时的处理,实际操作由DMA硬件直接执行完成。(注:DMA传送数据时,CPU不能使用总线)

通道(输入输出处理机IOP)进一步提高CPU效率,以增加更多的硬件为代价。实现对外围设备统一管理,完成外围设备与主存间的数据传送。

6、总线结构

总线是计算机设备与设备之间传输信息的公共数据通道,由总线上所有设备共享。

微机中总线分为数据总线(DB:传送数据信息,双向)、地址总线(AB:传送CPU的地址信息,单向)和控制总线(CB:传送控制信号、时序信号和状态信息等,每条线单向但整体双向)。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://yundeesoft.com/12575.html