大家好,欢迎来到IT知识分享网。

之前想要验证zynq通过serdes传输数据的实验,网上找了一篇文章,照着做了,没有一篇能完全实现,到了关键的地方都是一笔带过,大量的篇幅在讲DC平衡、高速信号产生串扰的原理,其实这些内容应该放在原理性的文章中。看到这种类型的文章,读者只想按部就班的把实验做出来。以下的内容就是基于这个思想的。

1、vivado工程的创建:

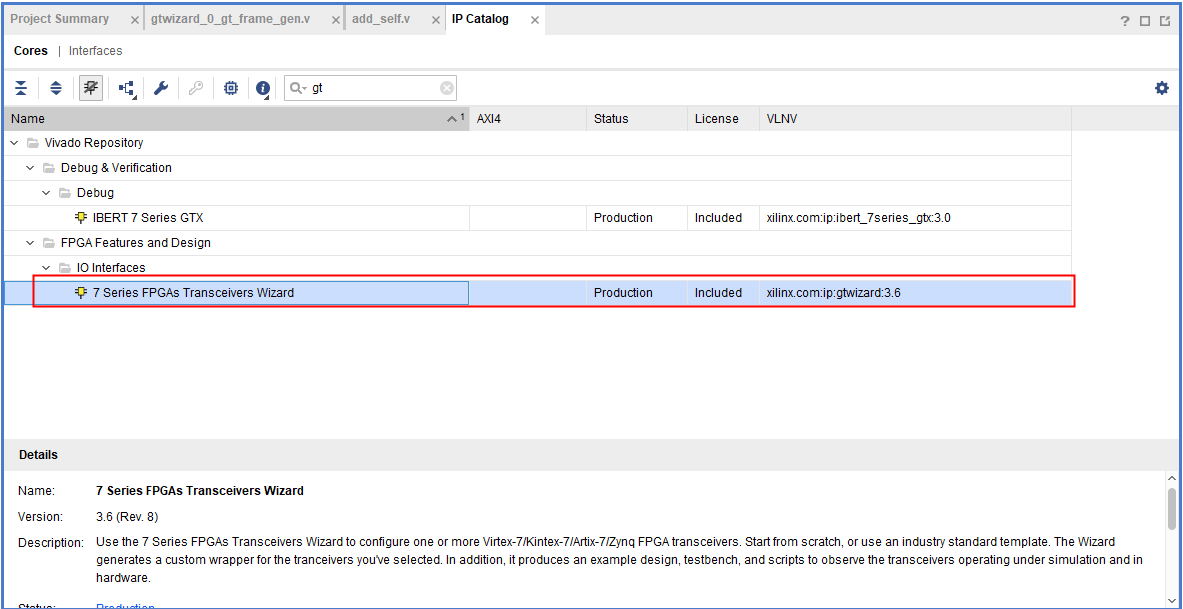

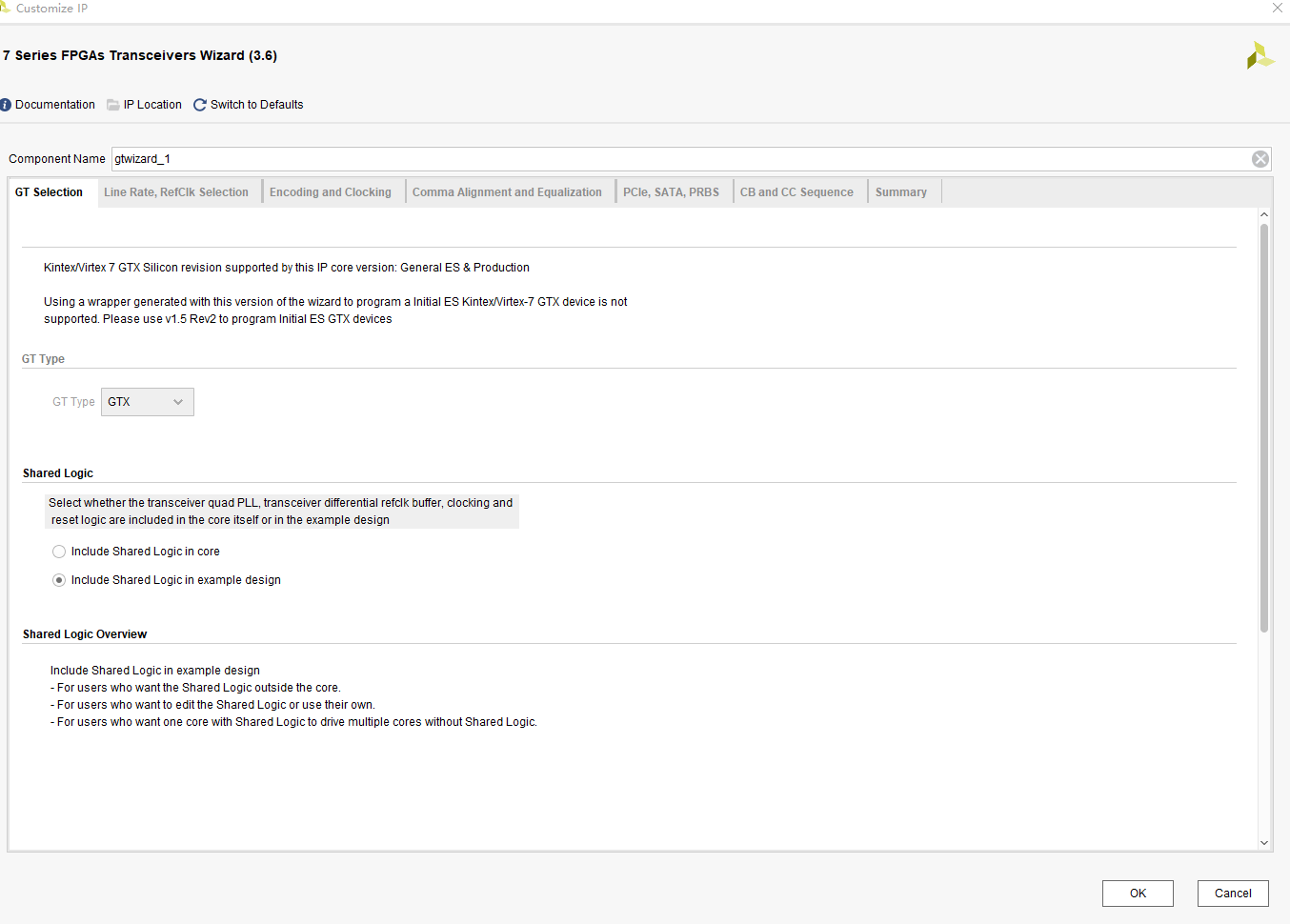

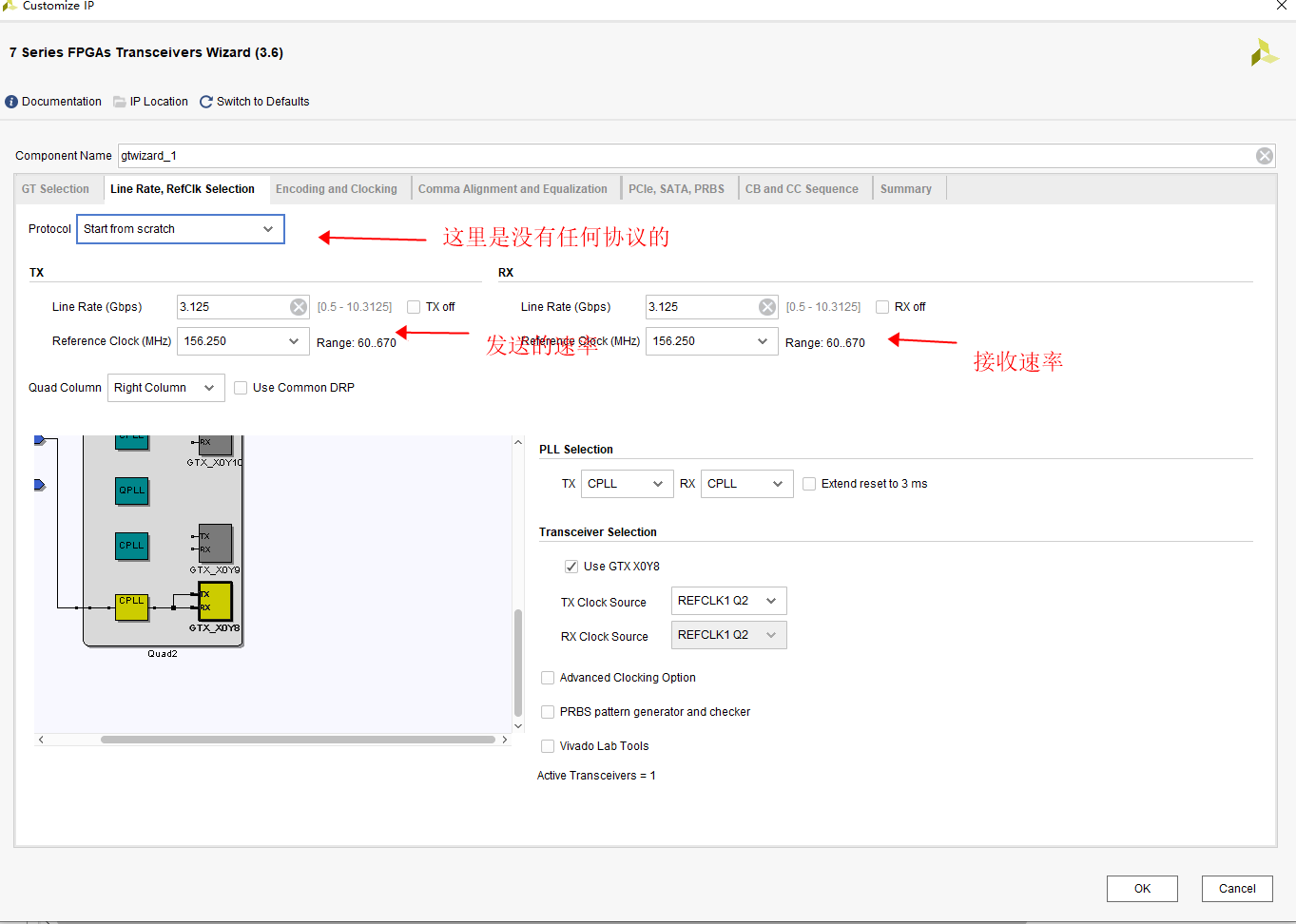

在ip Catalog 中找到如下图的IP,双击

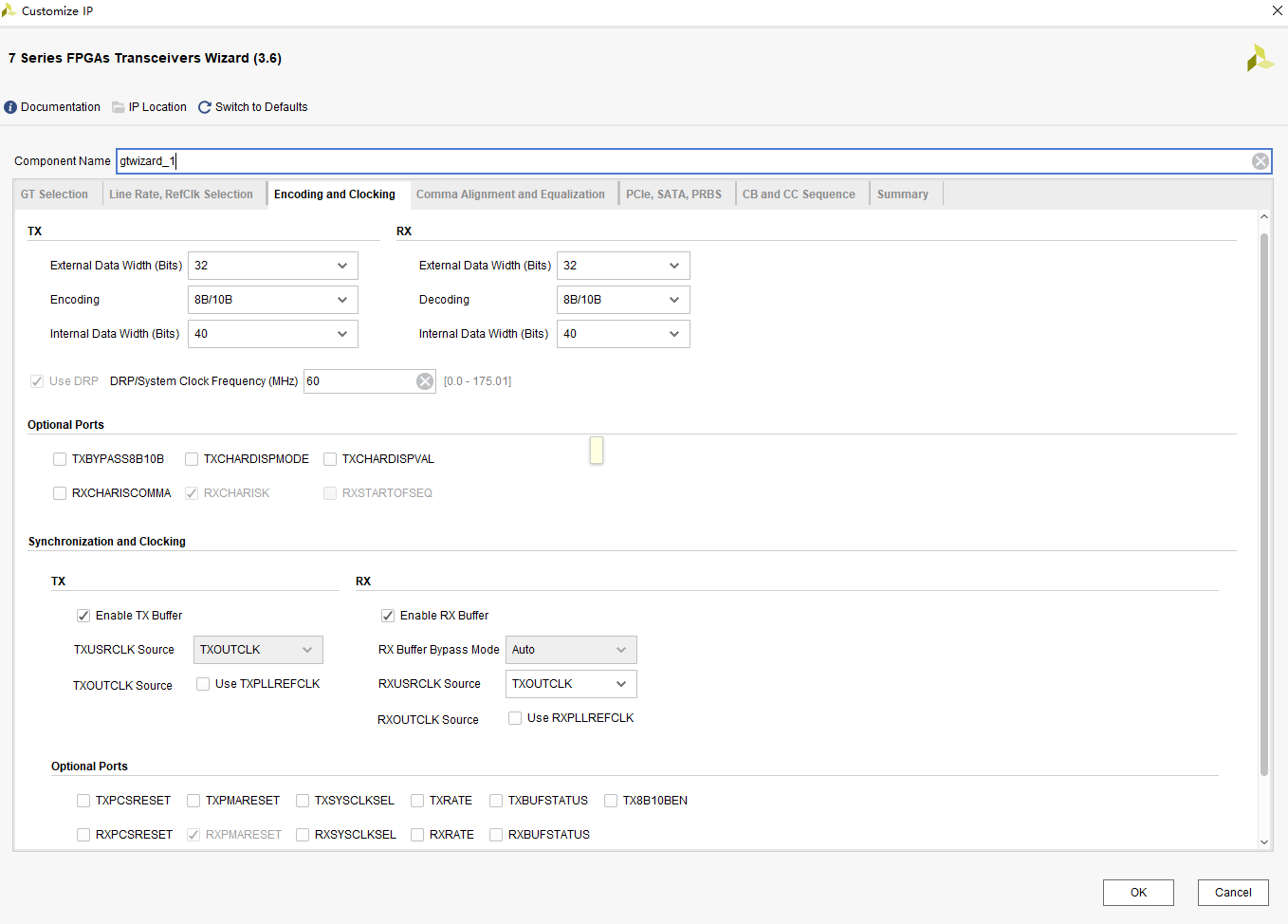

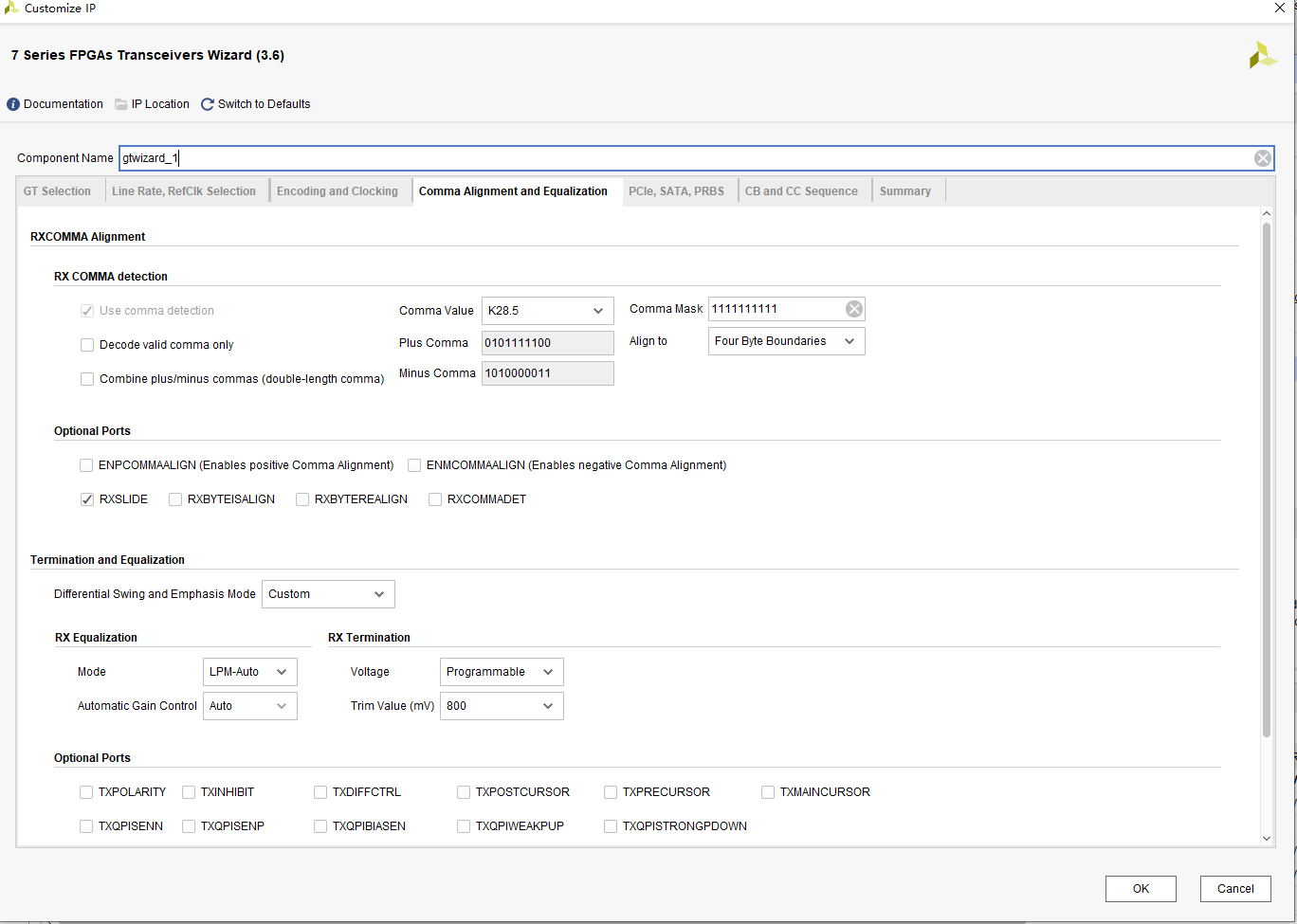

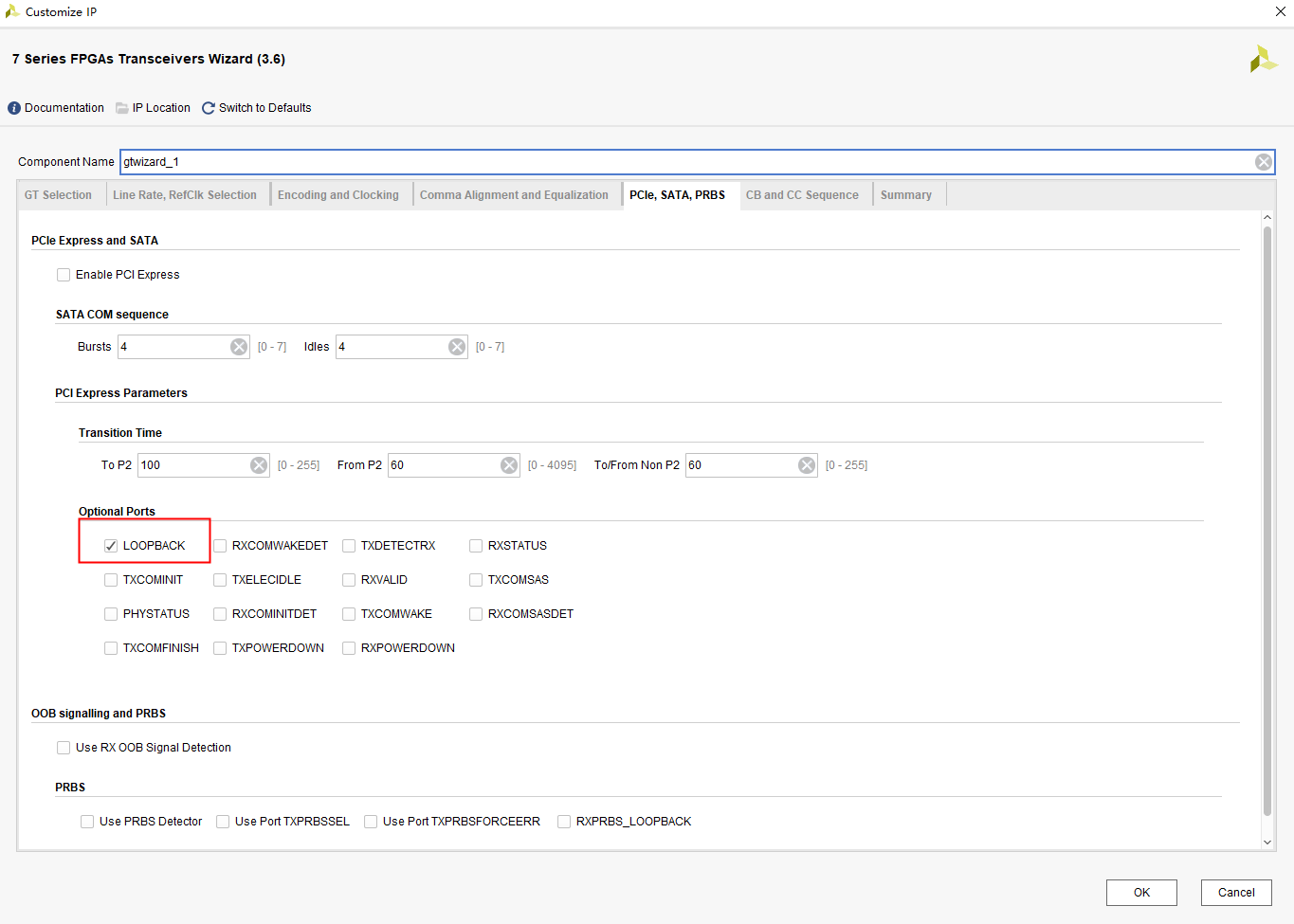

直接点击OK,打开example project。需要修改几个地方:

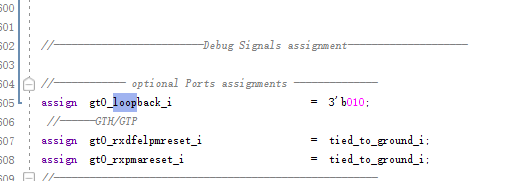

这个是设置远端回环的,如果是000则不使用回环。具体各个位怎么设置其他的文章很容易找到。这里的010就能满足本次实验。

还需要自己写一段测试代码,用来产生测试数据:

module add_self(

// User Interface

output reg [79:0] TX_DATA_OUT,

output reg [7:0] TXCTRL_OUT,

// System Interface

input wire USER_CLK,

input wire SYSTEM_RESET

);

reg [63:0] data;

reg [7:0] tx_ctrl_i;

(* ASYNC_REG = "TRUE" *) (* keep = "true" *) reg system_reset_r;

(* ASYNC_REG = "TRUE" *) (* keep = "true" *) reg system_reset_r2;

//___________ synchronizing the async reset for ease of timing simulation ________

always@(posedge USER_CLK)

begin

system_reset_r <= SYSTEM_RESET;

system_reset_r2 <= system_reset_r;

end

parameter DATA_LEN = 7'd100;

parameter START_FREAM = 3'b001;

parameter USER_DATA = 3'b010;

parameter IDEL = 3'b100;

reg [ 3:0]current_state;

reg [ 3:0]next_state;

reg [31:0]user_data;

wire send_finish=1'b0;

//时序电路,状态转换

always@(posedge USER_CLK)

begin

if(system_reset_r2)

current_state<=IDEL;

else

current_state<=next_state;

end

//组合电路,根据条件控制转换状态

always@(*)

begin

case(current_state)

IDEL:

if(!system_reset_r2)

next_state=START_FREAM;

else

next_state=IDEL;

START_FREAM:

next_state=USER_DATA;

USER_DATA:

if(send_finish) //传输完成,发送下一个bound

next_state=START_FREAM;

else if(system_reset_r2)

next_state=IDEL;

else if(user_data==DATA_LEN)

next_state=START_FREAM;

else

next_state=USER_DATA;//循环发送数据

default:next_state=IDEL;

endcase

end

//data gen

always@(posedge USER_CLK)

begin

if(system_reset_r2)

user_data<=32'b0;

else if(current_state == USER_DATA && user_data<DATA_LEN)

user_data<=user_data+1'b1;

else

user_data<=32'b0;

end

//send data

always@(posedge USER_CLK)

begin

if(system_reset_r2)

begin

TX_DATA_OUT<=80'h0;

TXCTRL_OUT<=80'h0;

end

case(current_state)

IDEL:

begin

TX_DATA_OUT<=80'h0;

TXCTRL_OUT<=8'h0;

end

START_FREAM:

begin

TX_DATA_OUT<=80'h00000000060504bc0100;

TXCTRL_OUT<=8'h01;

end

USER_DATA:

begin

TX_DATA_OUT<={32'h0,user_data[31:0],16'h0};

TXCTRL_OUT<=8'h0;

end

default:

begin

TX_DATA_OUT<=80'h0;

TXCTRL_OUT<=16'h0;

end

endcase

end

endmodule

我写的比较随意,有兴趣的可以自己按照自己的想法来写。好了,按照以上的步骤就能做一个简单的高速通信实验。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://yundeesoft.com/24148.html